# The Complete Electronics Lab for Windows

# **USERS MANUAL**

# COPYRIGHTS

© Copyright 1990-2019 DesignSoft, Inc. All rights reserved.

All programs and Documentation of TINA, and any modification or copies thereof are proprietary and protected by copyright and/or trade secret law.

# LIMITED LIABILITY

*TINA*, together with all accompanying materials, is provided on an "as is" basis, without warranty of any kind.

DesignSoft, Inc., its distributors, and dealers make no warranty, either expressed, implied, or statutory, including but not limited to any implied warranties of merchantability or fitness for any purpose.

In no event will DesignSoft Inc., its distributor or dealer be liable to anyone for direct, indirect, incidental or consequential damages or losses arising from the purchase of *TINA* or from use or inability to use *TINA*.

#### TRADEMARKS

Windows is a registered trademark of Microsoft Corporation. PSpice is a registered trademark of Cadence Design Systems, Inc. CorelDRAW is a registered trademark of Corel Inc. TINA is a registered trademark of DesignSoft, Inc.

\* English version

# TABLE OF CONTENTS

| 1.    | INTRODUCTION                                 | 9  |

|-------|----------------------------------------------|----|

| 1.1   | What is TINA and TINA Design Suite?          | 9  |

| 1.2   | Available Program Versions                   | 18 |

| 1.3   | Optional supplementary hardware              | 20 |

| 1.3.1 | TINALab II High Speed                        |    |

|       | Multifunction PC Instrument                  | 20 |

| 1.3.2 | LabXplorer Multifunction Instrument for      |    |

|       | Education and Training with Local and Remote |    |

|       | Measurement capabilities                     | 21 |

| 2.    | NEW FEATURES IN TINA                         | 23 |

| 2.1   | List of new features in TINA v12             | 23 |

| 2.2   | List of new features in TINA v11             | 25 |

| 2.3   | List of new features in TINA v10             | 26 |

| 2.4   | List of new features in TINA v9              | 27 |

| 2.5   | List of new features in TINA v8              | 28 |

| 2.6   | List of new features in TINA v7              | 29 |

# Allice Messtechnik GmbH

-0

# Contents

| 3.      | INSTALLATION AND START-UP                  | 31   |

|---------|--------------------------------------------|------|

| 3.1     | Installation Procedure                     | . 31 |

| 3.1.1   | Minimum hardware and software              |      |

|         | requirements                               | . 31 |

| 3.1.2   | Installation from CD-ROM or from the Web   | . 32 |

| 3.1.3   | Following the Installation Steps           | . 33 |

| 3.1.4   | Welcome and Software License               |      |

|         | Agreement                                  | . 33 |

| 3.1.5   | Entering User Information                  | . 34 |

| 3.1.6   | Platform Selection                         | . 35 |

| 3.1.7   | Single User License and Networking Options | . 35 |

| 3.1.7.  | 1 Single user license                      | 35   |

| 3.1.7.2 | 2 Network license installed on local PCs   | 35   |

| 3.1.7.3 | 8 Network license installed on file server | 35   |

| 3.1.8   | Choose Destination Location                | . 36 |

| 3.1.9   | Selecting a Setup Type                     | . 37 |

| 3.1.9.1 | I Typical                                  | 38   |

| 3.1.9.2 | 2 Compact                                  | 38   |

| 3.1.9.3 | 3 Custom                                   | 38   |

| 3.1.10  | Selecting the Program Folder               | . 39 |

| 3.1.11  |                                            |      |

| 3.1.12  |                                            |      |

| 3.1.13  | 3 Final check and copying the files        | . 41 |

| 3.1.14  | Completing the Setup                       | . 41 |

| 3.2     | Uninstalling TINA                          |      |

| 3.3     | Maintaining or Repairing an Installation   |      |

| 3.4     | Network Installation                       |      |

| 3.5     | Copy Protection                            |      |

| 3.5.1   | Copy Protection by Software                |      |

| 3.5.2   | Copy Protection by Hardware (dongle)       |      |

| 3.6     | Starting Up                                | . 50 |

| 3.7     | Experimenting with Example Circuits,       |      |

|         | avoiding common problems                   | . 50 |

|         |                                            |      |

| Contents |

|----------|

|          |

| 4.         | GETTING STARTED                                                   | 53    |

|------------|-------------------------------------------------------------------|-------|

| 4.1        | Schematic Editing Using the Mouse                                 | 53    |

| 4.1.1      | Using the right mouse button                                      |       |

| 4.1.2      | Using the left mouse button                                       |       |

| 4.1.2      | Measurement Units                                                 |       |

| 4.2<br>4.3 |                                                                   |       |

|            | The Basic Screen Format                                           |       |

| 4.4        | Placing the Circuit Components                                    |       |

| 4.4.1      | Wire                                                              |       |

| 4.4.2      | Input and Output                                                  |       |

| 4.5        | Exercises                                                         |       |

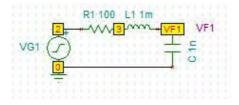

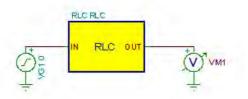

| 4.5.1      | Editing an RLC Circuit Schematic                                  |       |

| 4.6        | Analyses                                                          | . 68  |

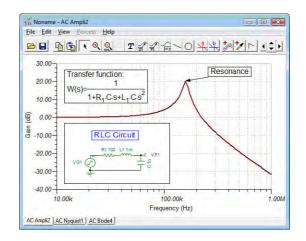

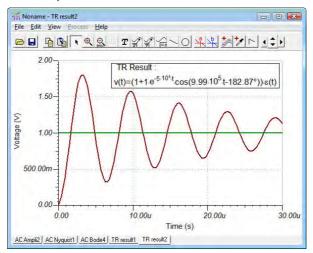

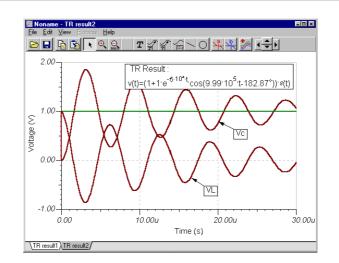

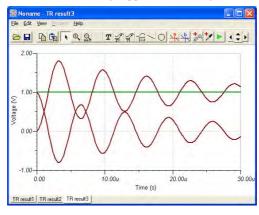

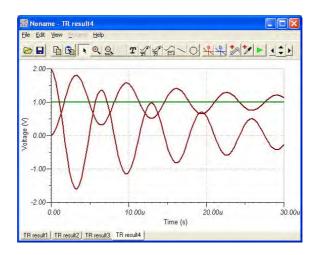

| 4.6.1      | Analyzing an RLC Circuit (DC, AC Transient and                    |       |

|            | Fourier analysis)                                                 | . 70  |

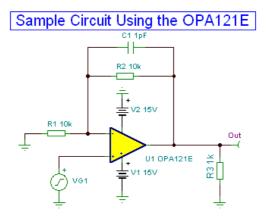

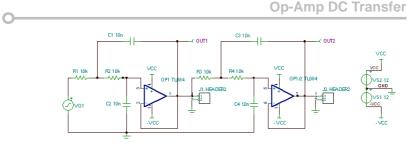

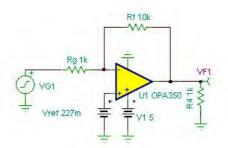

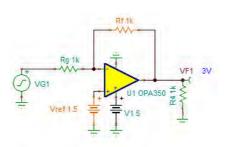

| 4.6.2      | Creating and analyzing an OP-AMP circuit                          | . 82  |

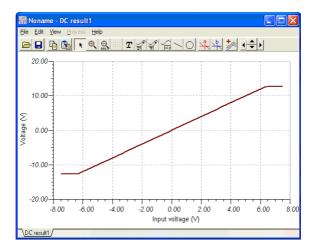

| 4.6.2.1    | I Calculating DC Transfer characteristic                          | . 87  |

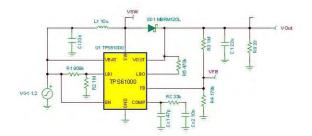

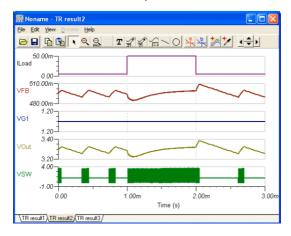

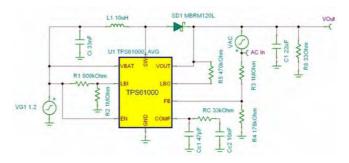

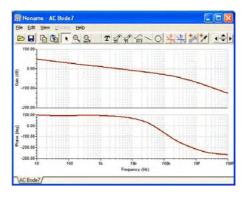

| 4.6.3      | Analysis of SMPS circuits                                         | . 88  |

| 4.6.4      | Power dissipation and efficiency calculations                     | . 99  |

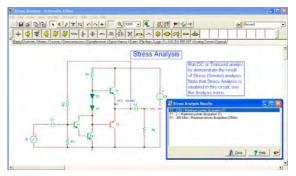

| 4.6.5      | Stress Analysis                                                   | . 102 |

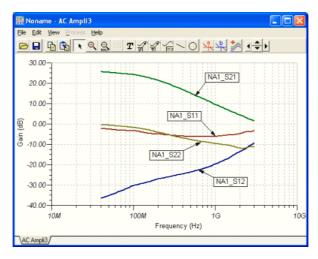

| 4.6.6      | Network Analysis                                                  | . 103 |

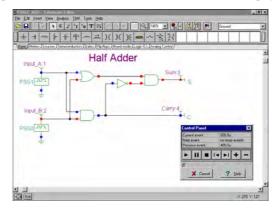

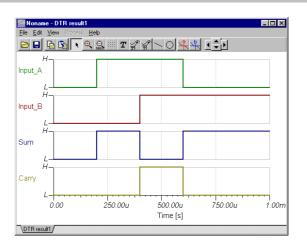

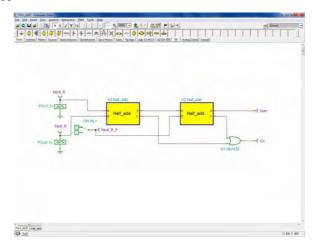

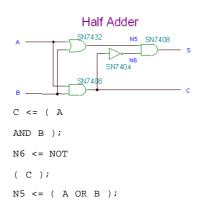

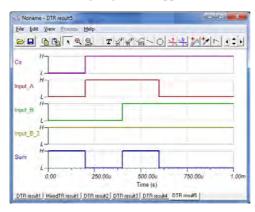

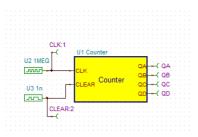

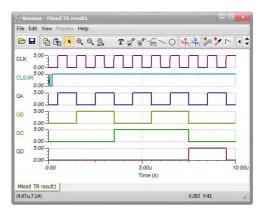

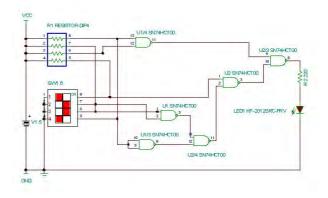

| 4.6.7      | Analyzing a Digital Circuit with TINA's                           |       |

|            | Digital Engine                                                    | . 104 |

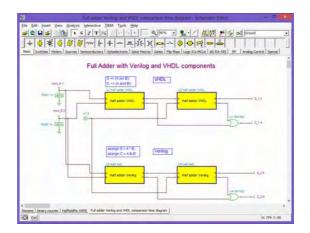

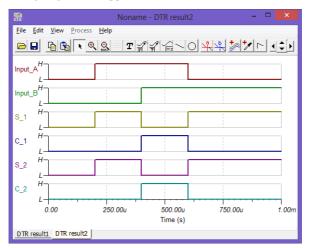

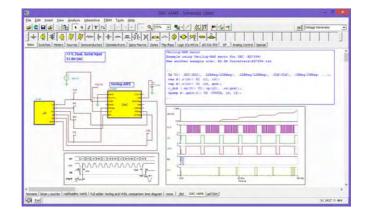

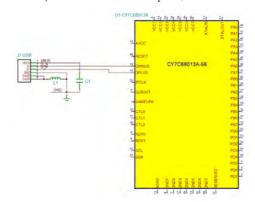

| 4.6.8      | Analyzing Circuits using HDL Models                               | . 106 |

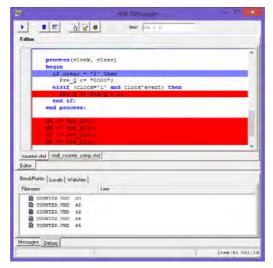

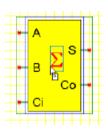

| 4.6.8.′    | Analyzing a Digital Circuit Using Digital VHDL<br>Simulation      | . 106 |

| 4.6.8.2    | 2 The HDL Debugger                                                | . 114 |

| 4.6.8.3    | 3 Analyzing a Digital Circuit Using Digital Verilog<br>Simulation | . 111 |

| 4.6.8.4    | Analyzing Circuits Using Verilog-A models                         | . 115 |

| 4.6.8.5    | 5 Analyzing Circuits Using Verilog-AMS models                     | . 116 |

| 4.6.8.6    | 6 Analyzing Circuits Using SystemC                                | . 118 |

-0

# Contents

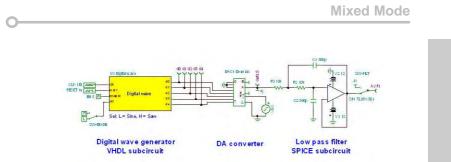

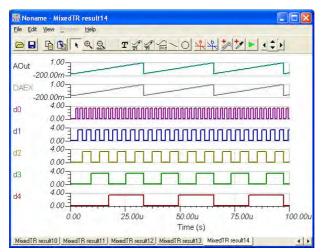

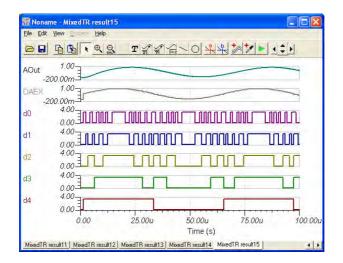

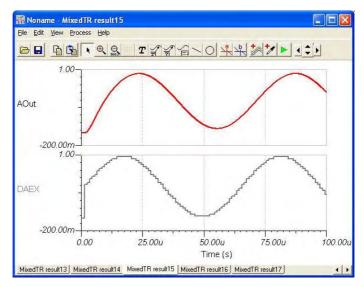

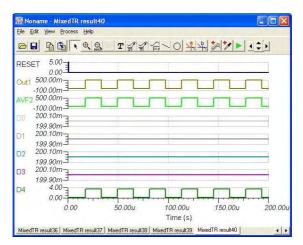

| 4.6.9     | Mixed Mode Simulation 132                           |

|-----------|-----------------------------------------------------|

| 4.6.9.1   | Waveform generation with a VHDL and Spice           |

|           | subcircuits                                         |

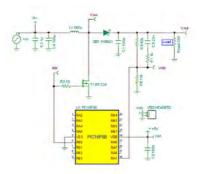

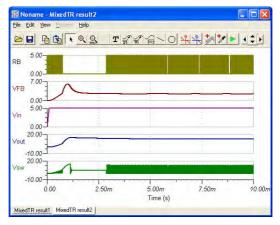

| 4.6.9.2   | MCU controlled SMPS circuit                         |

| 4.6.10    | Testing your circuit in interactive mode 139        |

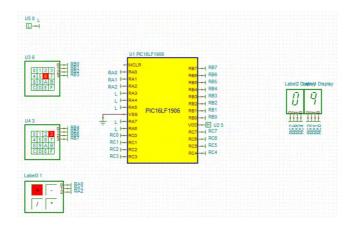

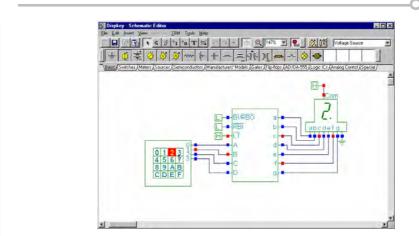

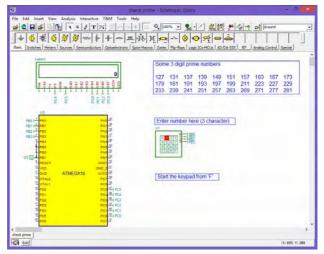

| 4.6.10.1  | Digital Circuit with a Keypad 140                   |

| 4.6.10.2  | Light Switch with Thyristor 141                     |

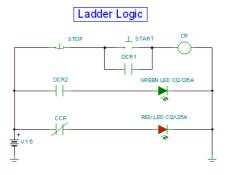

| 4.6.10.3  | Ladder Logic networks 141                           |

| 4.6.10.4  | HDL Circuits 142                                    |

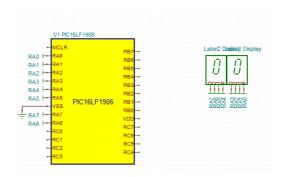

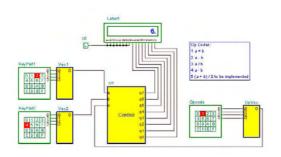

| 4.6.10.5  | Microcontroller (MCU) Circuits 144                  |

| 4.6.10.6  | Using the ASM Debugger 146                          |

| 4.6.10.7  | Example PIC Innterupt handling 149                  |

| 4.6.10.8  | Editing the ASM Code in the Debugger 151            |

| 4.6.10.9  | Making a Breakpoint in ASM 152                      |

| 4.6.10.10 | Programming MCUs using C 153                        |

| 4.6.10.11 | Debugging C code in MCUs 156                        |

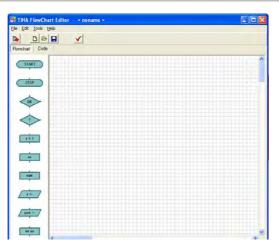

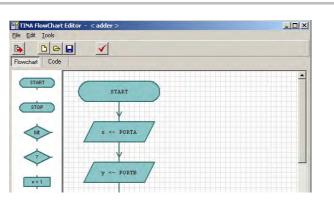

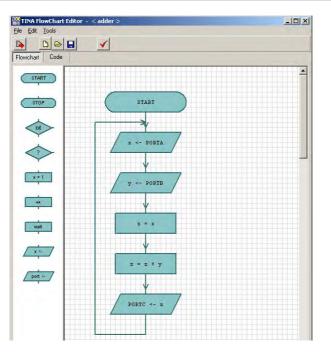

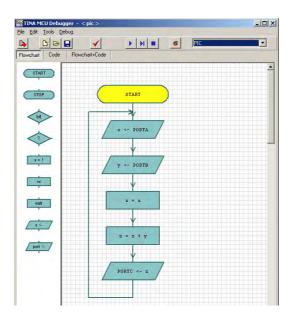

| 4.6.11    | Using the Flowchart Editor and Debugger in TINA 159 |

| 4.6.11.1  | Flowchart Editor 159                                |

| 4.6.11.2  | Flowchart Debugger 164                              |

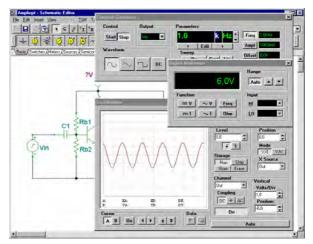

| 4.6.12    | Testing Your Circuit with Virtual                   |

|           | and Real Time Instruments 165                       |

| 4.6.13    | Using the Design Tool in TINA 168                   |

| 4.6.14    | Design Tool vs. Optimization in TINA 172            |

| 4.6.15    | Live 3D Breadboard 172                              |

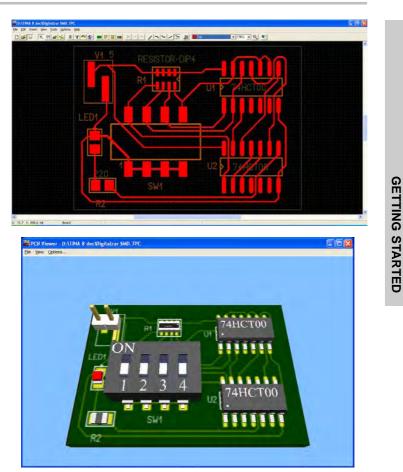

| 4.7 Cr    | eating a PCB (Printed Circuit Board) 178            |

| 4.7.1     | Setting and checking footprint names 178            |

| 4.7.2     | Invoking TINA PCB                                   |

| 4.7.3     | Multiple Logic Gates in the Same Package            |

|           | and their Power Supply 188                          |

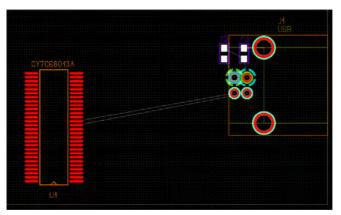

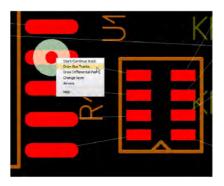

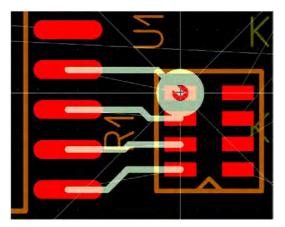

| 4.7.4     | Differential pair routing 191                       |

| 4.7.5     | Creating Buses in the Schematic Editor              |

|           | and the PCB Designer of TINA 197                    |

| 4.7.6     | Creating a Flexible PCB Layout (Flex PCB) 204       |

# Allice Messtechnik GmbH

| 0—      |                                                  | Contents |

|---------|--------------------------------------------------|----------|

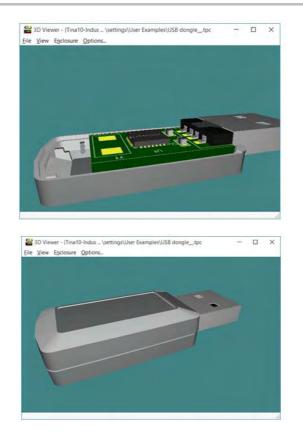

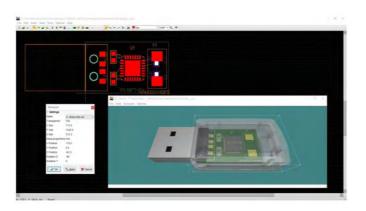

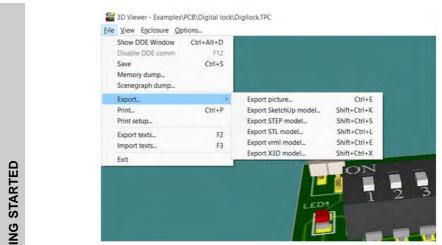

| 4.7.7   | Adding 3D Enclosure to your PCB Design           | 209      |

| 4.7.8   | 3D Export of your PCB Design                     | 211      |

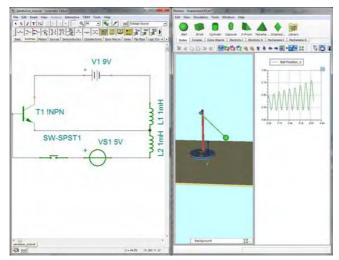

| 4.8     | Mechatronics Extension                           | 212      |

| 5.      | USING SUBCIRCUITS,                               |          |

|         | SPICE MACROS AND S-PARAMETERS                    | 219      |

| 5.1     | Making a Macro from a                            |          |

|         | schematic                                        | 219      |

| 5.2     | Making a Macro from a                            |          |

|         | Spice subcircuit                                 | 226      |

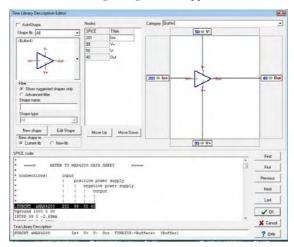

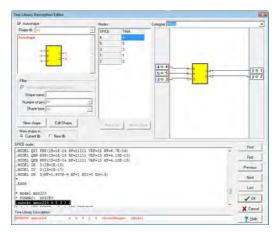

| 5.2.1   | Creating Spice Macros in TINA                    | 226      |

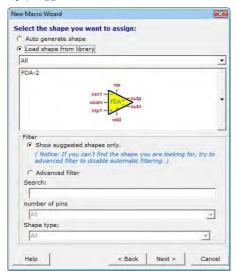

| 5.2.1.  | Creating macros from downloaded files            | 226      |

| 5.2.1.2 | 2 Creating macros on-the-fly by browsing the web | 228      |

| 5.2.2   | Adding Parameters to Spice Macros                | 236      |

| 5.3     | Using and extending Manufacturers'               |          |

|         | Spice model catalogs in TINA                     | 237      |

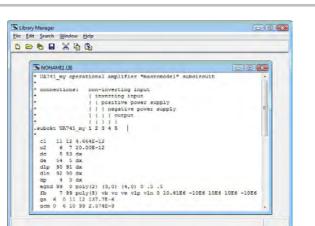

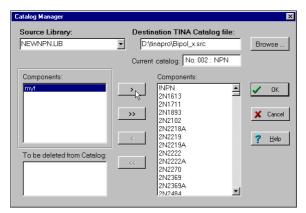

| 5.3.1   | Using the Library Manager                        | 238      |

| 5.3.1.  | I Introduction to Adding Spice macros to         |          |

|         | TINA libraries                                   | 238      |

| 5.3.1.2 | 2 Problems and solutions while adding            |          |

|         | Spice macros to TINA                             | 243      |

| 5.3.1.3 |                                                  | 050      |

| E 4     | to the library                                   |          |

| 5.4     | Adding S-parameter models                        |          |

| 5.5     | Making an HDL macros                             |          |

| 5.5.1   | Placing a HDL macro in the schematic editor      |          |

| 5.5.2   | Testing a HDL macro                              |          |

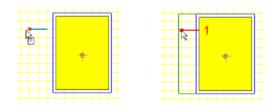

| 5.5.3   | Changing the pin arrangement of a HDL macro      | ∠00      |

-0

# Contents

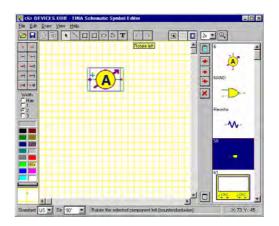

| 6.  | MAKING YOUR OWN SCHEMATIC SYMBOLS            |

|-----|----------------------------------------------|

|     | AND FOOTPRINTS 263                           |

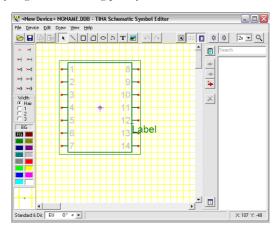

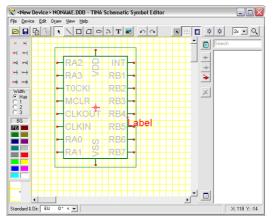

| 6.1 | Schematic Symbol Editor                      |

| 6.2 | IC Wizard in the Schematic Symbol Editor 267 |

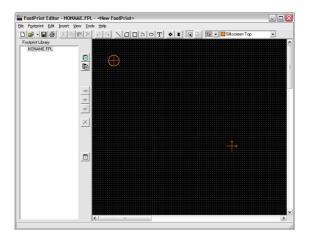

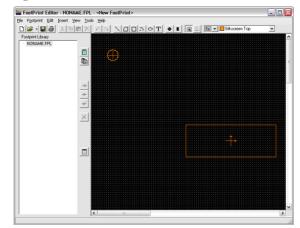

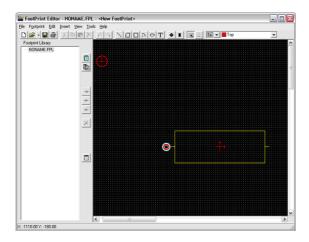

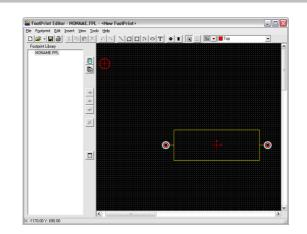

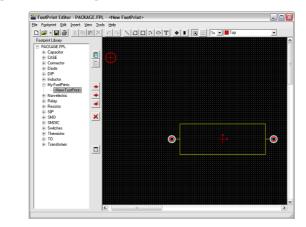

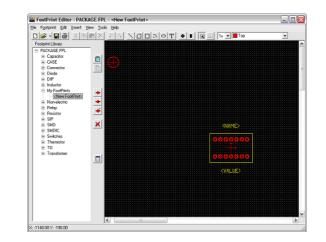

| 6.3 | Footprint Editor                             |

| 6.4 | IC Wizard in the Footprint Editor 272        |

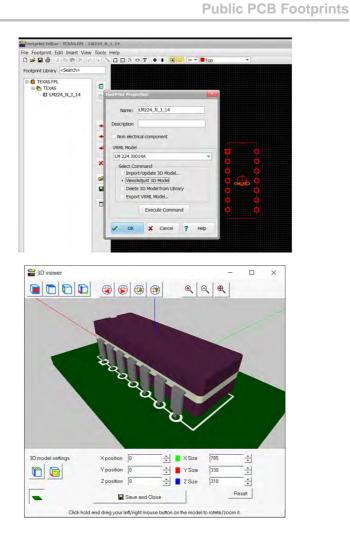

| 6.5 | Adding Public PCB Footprints to TINA 274     |

| 6.6 | Adding Public 3D Footprints to TINA 276      |

| 7.  | USING THE PARAMETER EXTRACTOR 279            |

| 8.  | ADVANCED TOPICS 283                          |

| 8.1 | Introduction                                 |

| 8.2 | Table of Contents of Advanced Topics 284     |

# CHAPTER 1

# 1.1 What is TINA and TINA Design Suite?

TINA Design Suite is a powerful yet affordable software package for analyzing, designing and real time testing of circuits with analog, digital & microcontroller components and components defined in various Hardware Description Languages, VHDL, Verilog, Verilog A, Verilog AMS and SystemC and for designing their PCB layouts. You can also analyze RF, communication, optoelectronic circuits and mechatronics applications with 3D interface.

Every year, electronic circuits become faster and more complex, and therefore require more and more computational power to analyze their operation. To meet this requirement DesignSoft engineers have included the ability to utilize the increasingly popular scalable multi-thread CPUs.

Since v12 TINA is available both in 64-bit and 32-bit editions. If you purchase TINA both versions are provided. The 64-bit version finally resolves the memory issues you may have experienced with large project.

Since 2013 TINACloud, the online version of TINA is also available. If you have licenses for both products, you can store your designs on the web and run anytime on any platforms without installation, including PCs, Macs, thin clients, tablets, smart phones, smart TVs and e-book readers. The program will run on our powerful web server with the same high speed whether you use a laptop, tablet or just a smartphone. You can then smoothly download your design from the web to your PC. Should you change something while you are on the road, continue the development off-line and upload your design again. Now TINACloud also includes a new online schematic editor with instant automatic saving of any changes you make and intgegrated PCB designer.

In TINA 10 and later versions you can create and simulate multidisciplinary designs. Disciplines now include electronics, 3D mechanics and control engineering. This opens a rich new field of applications in automotive engineering, sensing and control, automation, robotics and more.

A unique feature of TINA permits you to bring your circuit to life with the optional USB controlled TINALab II and LabXplorer hardware turn your computer into a powerful, multifunction T&M instrument. With LabExplorer, you can carry out remote measurement which is great for distance education.

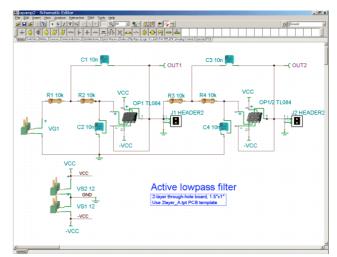

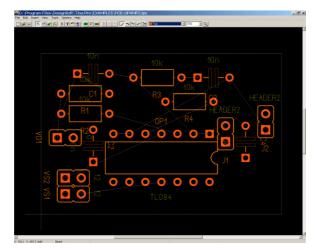

TINA is distributed in two major versions – TINA Standard and TINA Design Suite. TINA Standard includes circuit simulation only, while TINA Design Suite also includes the advanced PCB designer. This fully integrated layout module has all the features you need for advanced PCB design, including Multilayer flexible PCB's with split power planes, powerful autoplacement & autorouting, rip-up and reroute, manual "follow-me" trace placement, DRC, forward and back annotation, pin and gate swapping, keep-in and keep-out areas, thermal relief, fanout, plane layers, Gerber file output and much more. TINA and TINA Design Suite also have different editions tailored to customer needs. Some HDL languages and the Mechatronics extension are optional. Both the Standard and the Design Suite versions are provided in 64-bit and 32-bit editions.

TINA can also be used in the training environment. It includes unique tools for testing students' knowledge, monitoring progress and introducing troubleshooting techniques. With optional hardware it can be used to test real circuits for comparison with the results obtained from simulation. Of great importance to educators, the package includes all the tools needed to prepare educational materials.

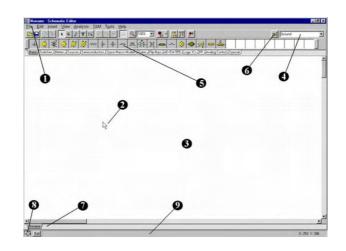

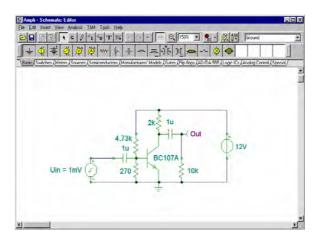

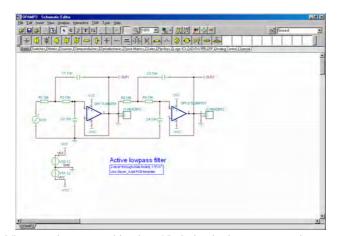

Schematic Capture. Circuit diagrams are entered using an easy to use schematic editor. Component symbols chosen from the Component bar are positioned, moved, rotated and/or mirrored on the screen by the mouse. TINA's semiconductor catalog allows the user to select components from a user-extendible library. An advanced "rubber wire" tool is provided allowing easy modification of the schematic diagrams. You can open any number of circuit files or

#### Introduction

subcircuits, cut, copy and paste circuit segments from one circuit into another, and, of course analyze any of the currently open circuits. TINA gives you tools to enhance your schematic by adding graphics elements such as lines, arcs, arrows, frames around the schematic, and title blocks. You can also draw non-orthogonal (diagonal) components such as bridges and 3-phase networks.

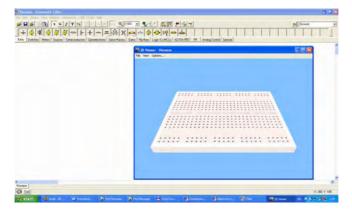

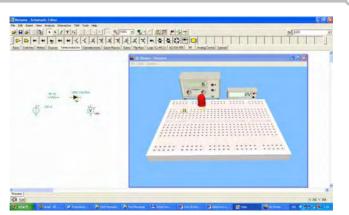

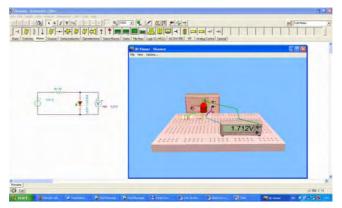

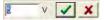

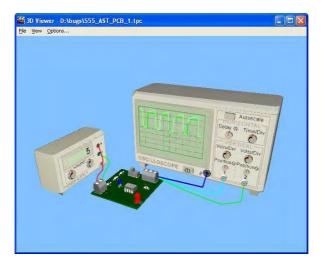

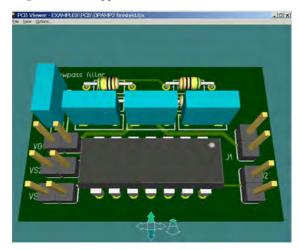

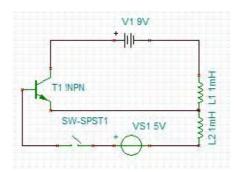

Live 3D Breadboard Tool. You can take your design for a solder-less breadboard (sometimes called a "whiteboard") and automatically build a life-like 3D picture of the breadboard. Now when you run TINA in interactive mode, virtual components such as switches, LEDs, instru- ments, etc. become "live" and will function with satisfying realism. Students will use the Live 3D Breadboard tool to prepare and docu- ment eye-catching lab experiments.

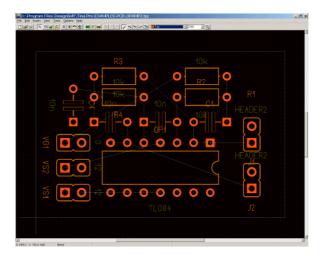

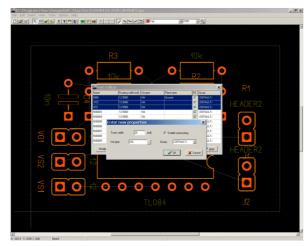

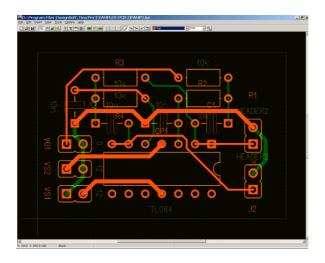

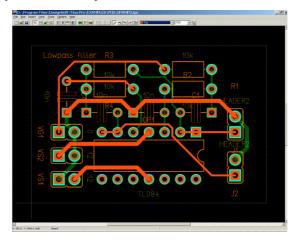

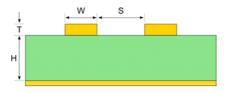

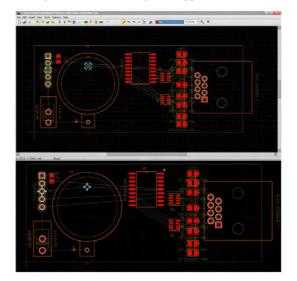

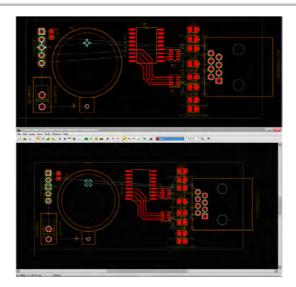

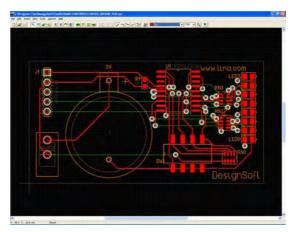

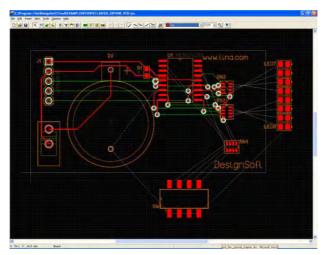

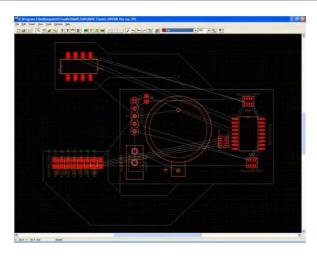

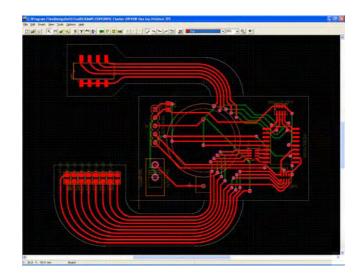

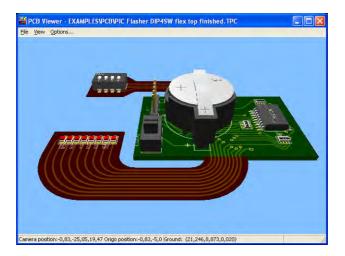

**PCB Design.** TINA Standard includes only circuit simulation, while TINA Design Suite includes TINA's advanced PCB designer. This fully integrated layout module has all the features you need for advanced PCB design, including Multilayer PCB's with split power planes, powerful autoplacement & autorouting, rip-up and reroute, manual and "follow-me" trace placement, DRC, forward and back annota- tion, pin and gate swapping, keep-in and keep-out areas, thermal relief, fanout, plane layers, bus & differential drawing tools, circuit block copying, 3D view from any angle, and much more. With TINA Design Suite you can prepare a PCB in at least two ways: using the G-Code control files to make in-house prototypes with milling machines using the G-Code control files provided by TINA; or sending Gerber files to PCB manufacturers.

**Electrical Rules Check** (ERC) will examine the circuit for questionable connections between components and display the results in the Electrical Rules Check window. ERC is invoked automatically, so missing connections will be brought to your attention before analysis begins.

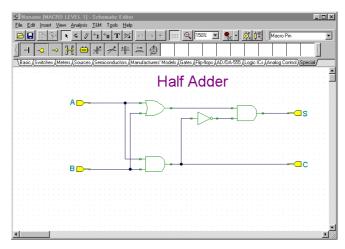

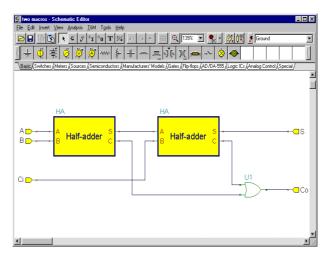

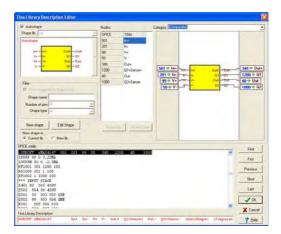

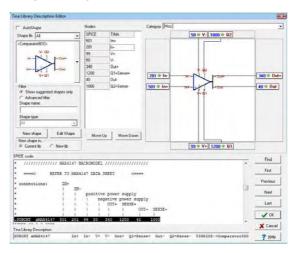

Schematic Symbol Editor. In TINA, you can simplify a schematic by turning portions of it into a subcircuit. In addition, you can create new TINA components from any Spice subcircuit, whether created by yourself, downloaded from the Internet, or obtained from a manufacturer's CD. TINA automatically represents these subcircuits as a rectangular block on your schematic, but you can create any shape you like with TINA's Schematic Symbol Editor.

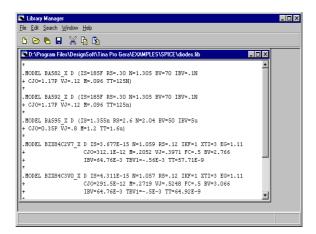

INRTODUCTION

Library Manager. TINA has large libraries containing Spice- and S-parameter models provided by semiconductor manufacturers such as Analog Devices, Texas Instruments, National Semiconductor, and others. You can add more models to these libraries or create your own Spice- and S-parameter library using TINA's Library Manager (LM).

**IBIS model Support.** IBIS (Input/output Buffer Information Specification) is a method to provide modeling information about the input/output buffers of integrated circuits. The good thing about IBIS models that they are often available even for devices where complete device models are not available from manufacturers. One of the most popular uses of IBIS models is Signal Integrity Analysis, including impedance matching and more. TINA currently supports the most widely used IBIS 4.2 version.

In TINA you can convert IBIS models to Spice macros and then use them in any circuits in TINA. You can also complete simplified digital device models e.g. MCUs with IBIS models to better describe their analog behavior. The use of IBIS models in detail is described in the Advance Topics Manual of TINA.

**Parameter Extractor.** Using TINA's Parameter Extractor you can also create component models that more closely represent actual real world devices by converting measurement or catalog data into model parameters.

**Text and Equation Editor.** TINA includes a Text and Equation Editor for annotating schematics, calculations, includes graphic output, and measurement results. It is an invaluable aid to teachers preparing problems and examples. You can also create popup texts wich are displayed when the cursor is moved above their title.

The circuit diagrams and the calculated or measured results can be printed or saved to files in standard Windows BMP, JPG, WMF and CFG format. These output files can be processed by a number of well known software packages (Microsoft Word, Corel Draw etc.). Netlists can be exported and imported in Pspice format and also to drive popular PCB packages such as ORCAD, TANGO, PCAD, PROTEL, REDAC and other programs.

**DC** analysis calculates the DC operating point and the transfer characteristic of analog circuits. The user can display the calculated and/ or measured nodal voltages at any node by selecting the node

#### Introduction

with the cursor. For digital circuits, the program solves the logic state equation and displays the results at each node step-by-step.

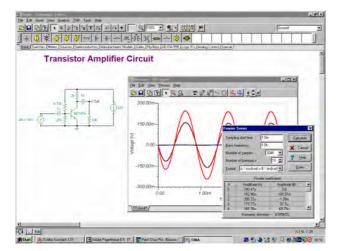

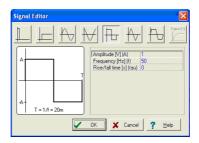

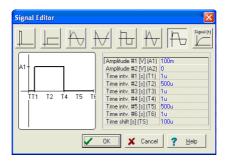

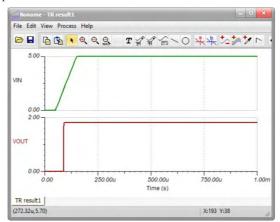

**Transient analysis.** In the transient and mixed mode of TINA you can calculate the circuit response to the input waveforms that can be selected from several options (pulse, unit step, sinusoidal, triangular wave, square wave, general trapezoidal waveform, .WAV file, White noise and user-defined excitation) and parameterized as required. For digital circuits, programmable clocks and digital signal generators are available. Power dissipation end efficiency calculations are also included.

Auto convergence. Convergence that is obtaining solution is one of the most complicated task in circuit simulation as due to the strongly nonlinear nature of electronic circuits. Although TINA is one of the best converging simulator software on the market sometimes manual parameter settings might be needed to achieve convergence. There are several analysis parameter sets are available to be used in case of convergence problems. In TINA 12 and later versions In TINA v12 and later versions these parameter sets are automatically applied in case of need and the user can also add more settings.

**Transient Noise Analysis.** Noise effects are usually simulated with linear AC noise analysis which is also available in TINA. However when the noise influences the system behavior in a nonlinear way, linear noise analysis is no more satisfactory and transient noise analysis that is simulation in the time domain is necessary. A few examples:

- · Analysis of systems with low signal-to-noise ratio

- · Noise analysis of oscillator circuits

- · Analysis of noise effects in digital circuits

The voltage and current generators of TINA now include a parameterizable white noise signal, and application circuits are available to generate other typical noise signals, which makes transient noise analysis possible.

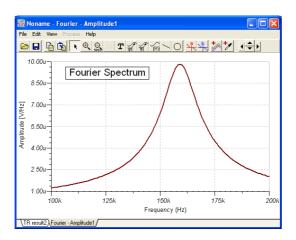

**Fourier analysis.** In addition to the calculation and display of the response, the coefficients of the Fourier series, the harmonic distortion for periodic signals, and the Fourier spectrum of non-periodic signals can also be calculated.

INRTODUCTION

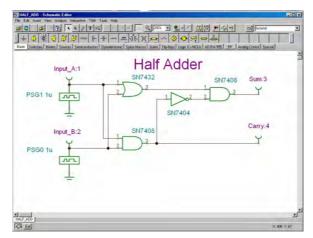

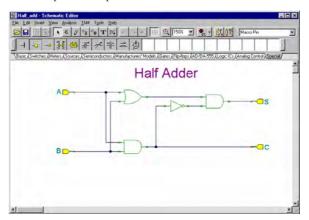

**Digital Simulation.** TINA now includes a very fast and powerful simulator for digital circuits. You can trace circuit operation step-by-step, forward and backward, or view the complete time diagram in a special logic analyzer window. In addition to logic gates, there are ICs and other digital parts from TINA's large component library.

HDL simulation. TINA now includes all major analog, digital and mixed Hardware Description Languages: VHDL, Verilog, Verilog A, Verilog AMS and SystemC to verify designs in analog, digital and mixed-signal analog-digital environments. Your circuits can contain editable HDL blocks from the libraries of TINA and Xilinx or other HDL components created by yourself or downloaded from the Internet. TINA compiles HDL into highly efficient machine code for speed optimization. You can freely combine HDL and Spice macros and the schematic components of TINA. Also you can edit the VHDL, Verilog, Verilog A&AMS source of HDL components then simulate and see the result instantly. With the built in HDL debugger you can execute VHDL, Verilog, Verilog A&AMS components step-by-step, add breakpoints, watchpoints, display variable information, etc. The SystemC source components you can edit and compile with MS Visual C and then add to TINA as high performance compiled components.

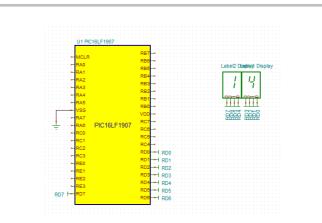

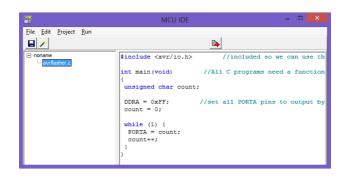

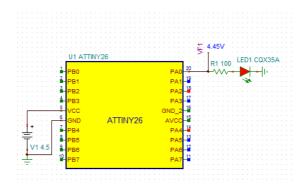

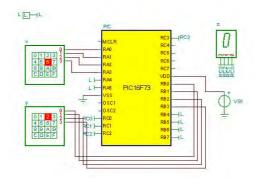

**Microcontroller (MCU) simulation.** TINA includes a wide range of microcontrollers (PIC, AVR, 8051, HCS, ARM, XMC) which you can test, debug and run interactively. The built in MCU assembler allows you to modify your assembler code and see the result promptly. You can also program and debug MCUs in C, using external C compilers including the MPLAB-XC compilers. In TINA v12 and later versions more than 1400 MCU models are are available in TINA for simulation and PCB design.

Flowchart Editor and Debugger. Writing MCU assembly code is often a hard and tedious task. You can simplify software development and gain more time to design the electronics hardware if, instead of manual coding, you use TINA's Flowchart editor and debugger to generate and debug the MCU code. This easy-to-use tool works with symbols and flow control lines with which you can represent the algorithm you want. TINA also supports other code generators, the free-of-charge XMC code generation platform DAVE

from Infineon Technologies and the FLOWCODE graphical programming language from Matrix Technology Solutions Limited.

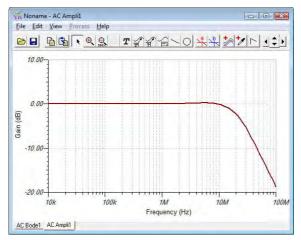

**AC analysis** calculates, complex voltage, current, impedance, and power can be calculated. In addition, Nyquist and Bode diagrams of the amplitude, phase and group delay characteristics of analog circuits can be plotted. You can also draw the complex phasor diagram. For non-linear networks, the operating point linearization is done automatically.

**Network analysis** determines the two-port parameters of networks (S, Z, Y, H). This is especially useful if you work with RF circuits. Results can be displayed in Smith, Polar, or other diagrams. The network analysis is carried out with the help of TINA's network analyzer. The RF models of the circuit elements can be defined as SPICE subcircuits (SPICE macros) which contain parasitic components (inductors, capacitors) or as an S-parameter model defined by its S (frequency) function. S functions are normally provided by the component manufacturers (based on their measurements) and can be downloaded from the Internet and inserted into TINA either manually or by using TINA's library manager.

Linear AC Noise Analysis determines the noise spectrum with espect to either the input or the output. The noise power and the signal-to-noise ratio (SNR) can also be calculated.

**Symbolic analysis** produces the transfer function and the closed form expression of the response of analog linear networks in DC, AC, and transient modes. The exact solution, calculated through the symbolic analysis, can also be plotted and compared to the numerically calculated or measured results. The built-in interpreter can evaluate and plot arbitrary functions.

Monte-Carlo and Worst-case analysis. Tolerances can be assigned to the circuit elements for use in Monte-Carlo and/or worst-case analyses. The results can be obtained statistically, and their expected means, standard deviations and yields can also be calculated.

**Design Tool** This powerful tool works with the design equations of your circuit to ensure that the specified inputs result in the specified output response. The tool offers you a solution engine that you can use to solve repetitively and accurately for various scenarios. The

INRTODUCTION

calculated component values are automatically set in place in the companion TINA schematic and you can check the result by simulation. This feature is also very useful for semiconductor and other electronics component manufacturers to provide application circuits along with the design procedure.

**Optimization.** TINA's enhanced optimization tool can tweak one or more unknown circuit parameters to achieve a predefined target response. The target circuit response (voltage, current, impedance, or power) must be "monitored" by meters. For example, you can specify several working point DC voltages or AC transfer function parameters and have TINA determine the values of the selected components.

**Post-processor.** Another great new tool of TIN A is its post-processor. With the post-processor, you can add new curves of virtually any node and component voltage or current to existing diagrams. In addition, you can post-process existing curves by adding or subtracting curves, or by applying mathematical functions to them. You can also draw trajectories; i.e., draw any voltage or current as a function of another voltage or current.

**Presentation.** With TINA you can make quality documents incorporating Bode plots, Nyquist, Phasor, Polar and Smith diagrams, transient responses, digital waveforms and other data using linear or logarithmic scales. Customize presentations easily using TINA's advanced drawing tools-you can print your plots directly from TINA, cut and paste them into your favorite word processing package, or export them to popular standard formats. Customization includes complete control over texts, axes, and plot style; e.g., setting line width and color, fonts in all sizes and color, and automatic or manual scaling for each axis. In TINA v12 and later versions the cursor display is integrated into the diagram window and it is possible to display all curves under the cursor.

Interactive mode. When everything is in order, the ultimate test of your circuit is to try it in a "real life" situation using its interactive controls (such as keypads and switches) and watching its displays or other indicators. You can carry out such a test using TINA's interactive mode. You can not only play with the controls, but you can also change component values while the analysis is in progress. In addition, you can assign hotkeys to component values and switches

#### Introduction

to change them simply by pressing a key. You will immediately see the effect of the change. You can also test MCU applications in TINA's interactive mode. You can not only run and test them using the several lifelike interactive controls e.g., keyboards, but you can also debug them while the MCU executes ASM code step by step, And displays the register contents and TINA's outputs in each step. If necessary you can modify the ASM code on the fly and test your circuit again without using any other tool.

Virtual instruments. In addition to standard analysis presentations such as Bode and Nyquist plots, TINA can present its simulation results on a wide range of high-tech virtual instruments. For example, you can simulate the time response of your circuit using a virtual square wave generator and a virtual oscilloscope. Using TINA's virtual instruments is a good way to prepare for the use of real test and measurement equipment. Of course it is important to remember that the "measurement results" obtained with virtual instruments are still simulated. From v11 TINA also includes virtual instruments (to be found under the Meters component tab) for Efficiency, Average values and Frequency.

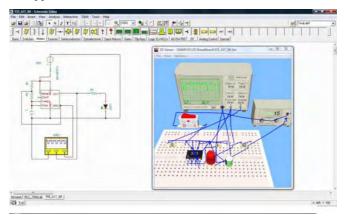

**Real-time Test & Measurements.** TINA can go beyond simulation when supplementary hardware is installed on the host computer. With this hardware, TINA's powerful tools can make real-time measurements on real circuits and display the results on its virtual instruments.

**Training and Examination.** TINA has special operating modes for training and for examination. In these modes, under TINA's control, the students solve problems assigned by the teacher. The solution format depends on the types of problems: they can be selected from a list, calculated numerically, or given in symbolic form. The interpreter - providing a number of solution tools - can also be used for problem solving. If the student cannot solve the problem, he/she can turn to the multilevel Advisor. The package includes all the tools needed to produce educational materials. A collection of examples and problems worked out by teachers is also part of the package. Another special educational function of TINA is the software or hardware simulation of circuit faults to practice troubleshooting. Using TINA, you can transform existing PC classrooms into contemporary electronics training labs at low cost.

INRTODUCTION

**Mechatronics Extension.** With this optional add-on package you can create and simulate multidisciplinary designs currently including electronics, 3D mechanics and control engineering. You can place light sources, light sensors, motors and actuators in TINA's mechanical window and connect with their counterparts in the analog, digital mixed electronic circuits. You can control the mechanics from the electronics part of TINA even with complex software written in C or assembly language, then compile and execute the code in the MCUs while running the electronic and 3D mechanical simulation simultaneously.

# 1.2 Available Program Versions

Different program versions, tailored to meet various needs, are available.

TINA is distributed in to major versions TINA and TINA Design Suite. TINA includes simulation only while TINA Design Suite includes our new advanced PCB designer too.

Both versions are available with the following features:

- **Industrial version:** Includes all of TINA's features and utilities.

- Network version: TINA can be used under most well known networks including Microsoft, Linux, Novell, Citrix and more. This feature is especially recommended for corporate and educational use.

- Educational version: It has most features of the Industrial version but parameter stepping and optimizations are allowed for one parameter only, Stress Analysis and the Steady State Solver are not included.

- **Classic Edition:** It has the same features as the Educational version above, except that Network Analysis is not allowed, TINA's large S-parameter component library and the Parameter Extractor, Stress Analysis and the Steady State Solver are not included. IBIS model support, Dissipation and Efficiency calculation and the Autoconvergence tool are not included.

#### Introduction

- **Student Version:** Has the same features as Classic Edition version except that the circuit size is limited to 100 nodes including internal Spice macro nodes. The number of pads on the PCB layout is also limited to 100. Global Parameters and HDL extensions are not allowed.

- **Basic version:** Has the same features as Classic Edition except that the circuit size is limited to 200 nodes including internal Spice macro nodes. The number of pads on the PCB layout is also limited to 200. Global Parameters and HDL extensions are not allowed.

- **Basic Plus version:** Has the same features as Classic Edition except that the circuit size is limited to 800 nodes including internal Spice macro nodes. The number of pads on the PCB layout is also limited to 800. Global Parameters and HDL extensions are not allowed.

#### **OPTIONS:**

- HDL Extension: Extends the default VHDL hardware description language in TINA with Verilog, Verilog A and Verilog AMS and SystemC.

- Mechatronics Extension add-on package: Create and simulate multidisciplinary designs simultaneously including electronics, 3D mechanics and control engineering.

INRTODUCTION

# 1.3 Optional supplementary hardware

# 1.3.1 TINALab II High Speed Multifunction PC Instrument

With TINALab II you can turn your laptop or desktop computer into a powerful, multifunction test and measurement instrument. Whichever instrument you need; multimeter, oscilloscope, spectrum analyzer, logic analyzer, arbitrary waveform generator, or digital signal generator it is at your fingertips with a click of the mouse. In addition TINALab II can be used with the TINA circuit simulation program for comparison of simulation and measurements as a unique tool for circuit development, troubleshooting, and the study of analog and digital electronics.

TINALab II includes a DC to 50MHz bandwidth, 10/12 bit resolution, dual-channel **Digital Storage Oscilloscope**. Due to its advanced equivalent-time sampling technology, TINALab can acquire any repetitive signal with up to **4GS/s equivalent sampling rate**, while in single shot mode the sampling rate is 20 MS/s. The full scale input range is  $\pm$ 80V, with 5mV to 20V/div ranges.

The synthesized **Function Generator** provides sine, square, ramp, triangle and arbitrary waveforms from DC to 4MHz, with logarithmic and linear sweep, and modulation up to 10V peak to peak. Arbitrary waveforms can be programmed via the high level, easy to use language of TINA's Interpreter. Working automatically in conjunction with the Function Generator, the **Signal Analyzer** measures and displays Bode amplitude and phase diagrams, Nyquist diagrams, and also works as **Spectrum Analyzer**.

Digital I/O for the high-tech **Digital Signal Generator** and Logic Analyzer instruments allow fast 16-channel digital testing up to 40MHz.

The optional **Multimeter** for TINALab II allows DC/AC measurements in ranges from 1mV to 100V and 100 mA to 1A. It can also measure DC resistance in ranges from 1 $\Omega$  to 1M $\Omega$ .

You can also plug **Experimenter Modules** into the slot on the front of TINALab II, allowing you to simulate, measure, and troubleshoot virtually the whole range of analog and digital electronics.

# Allice Messtechnik GmbH

#### Introduction

Using TINALab II with TINA gives you the unique capability to have circuit simulation and real time measurements in the same integrated environment. This provides an invaluable tool for troubleshooting and brings your designs to life by comparing simulated and measured results.

# 1.3.2 LabXplorer: Multifunction Instrument for Education and Training with Local and Remote Measurement capabilities

LabXplorer turns your desktop, laptop, tablet or smart phone into a powerful, multifunction test and measurement instrument for a wide range of applications. Instruments, whatever you need, are at your fingertips. LabXplorer provides multimeter, oscilloscope, spectrum analyzer, logic analyzer, programmable analog and digital signal generator, impedance analyzer and also measures characteristics of passive electronic components and semiconductor devices.

LabXplorer can be used with its virtual instruments both stand-alone or remotely through the Internet or LAN.

It also supports the TINA circuit simulation program and its cloud based version TINACloud for comparison of simulation and measurements as a unique tool for circuit development, troubleshooting, and the study of analog and digital electronics.

In remote mode Labexplorer's virtual instruments run on most OSs and computers, including PCs, Macs, thin clients, tablets--even on many smart phones, smart TVs and e-book readers. You can use LabXplorer remotely in the classroom, computer lab, at home, and, in fact, anywhere in the world that has internet access. LabXplorer comes with various, remotely programmable, plug-in analog, digital and mixed circuit experiment boards. INRTODUCTION

# CHAPTER 2 NEW FEATURES IN TINA

This chapter describes the new features and changes in the latest TINA v12 and also in the previous 11, 10, 9.x ,8.0 and 7 versions. Many of the new features were suggested by TINA users, while others were created by DesignSoft's team. We are sure you will share our excitement about these new features.

# 2.1 List of New features in TINA v12

- 32-bit and 64-bit versions

- Power dissipation and efficiency calculations

- IBIS model import and analysis

- Integrated cursor display in the diagram window

- Cursor displays for all curves in transient diagrams

- Syntax highlighting in Spice and HDL editors

- HDL library compilation and management

- Global parameter stepping

- Enhanced RF component insert dialog

- S-parameter wizard

- Spice control command editor (.AC, .DC, .NOISE, .TRAN)

- Enhanced support of PSpice format digital blocks

- Running Spice simulation from command line (external tool for netlist format)

- Running TINA from command line (.TSC format)

- Store last settings of virtual instruments

- Control for automatic separation of outputs in the diagram window

#### **New Features**

# NEW FEATURES

#### Convergence improvements

- Autoconverge (Transient simulation with system or user defined different parameter sets)

- Transient simulation with zero initial voltages if operating calculation fails

#### New device models

- New Delta-Sigma ADC devices

- BSIM3V3.2 model

- GaAs devices

- GaN devices

#### Advanced MCU support

- More than 500 MCUs, 1400 MCUs total

- PIC16 microcontrollers (222 devices)

- STM32 F4, F7 microcontroller support (227 devices)

- PIC18, PIC32 CAN interface support

- Texas Instruments Tiva C Series TM4C123x Cortex-M4 microcontroller support (51 devices)

- MCP23S17 I/O expander support

- Texas Instruments Sitara AM3358 processor support

- Serial Monitor window for monitoring serial communication

#### Other new features

- Interpreter functions for standard values for components (E series)

- Set global parameter as input of DC transfer calculation

- Add comments to design tool input parameters

- Hotkey editor define custom hotkeys

- Show partial result of transient simulation if simulation is aborted

- Advanced analysis control links

#### **PCB** Design

- Bus connection

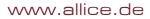

- Transmission line design (Differential pair)

- Block repetition (Macro-block copy)

# Allice Messtechnik GmbH

**New Features**

# 2.2 List of New features in TINA v11

- 8,000+ new parts, including power electronics devices

- SystemC support

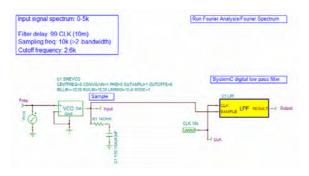

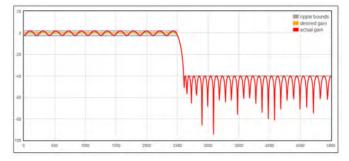

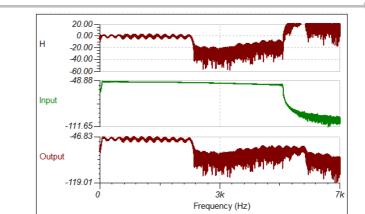

- Create Digital filters in SystemC and run in TINA

- Add MCUs in SystemC to TINA

- Infineon design folder with industrial designs

- Industrial Power, Lighting, Motor Control application circuits

- XMC microcontrollers and application circuits

- Support of the free-of-charge XMC code generation platform DAVE.

- Efficiency-, Average value-, and Frequency-meters

- Analysis control links

- Advanced Macro editing

- Advanced Macro editing

- SAR and Sigma-Delta ADCs

- DACs with SPI

- I2C, SPI bus simulation

- PM bus, SM bus simulation and monitors

- Transient Noise Analysis

- Transient Noise Generator

- Popup text

- DACs with SPIBSIM4 modelDACs with SPI

- Microchip XC8 compiler support

- FLOWCODE 7 support

- Arduino support

- Smart wire

- Enhanced I/O assignment

- Post processing of Fourier Spectrum

NEW FEATURES

#### **New Features**

- Export of Diagrams in CSD format (Common Simulation Data File)

- Advanced "Remember diagram settings" option, saved with the circuit

#### **PCB** Design

- Importing in 3D Enclosure models in industry standard formats

- Visualization of PCB design with Enclosures in 3D

- Exporting PCB with Enclosure in industry standard formats

- 3D printer support

- Importing Footprints in 2D and 3D in industry standard formats

# 2.3 List of New features in TINA v10

- Windows 8 compatibility

- Open project files with preview of schematics and mechatronics

- Edif import

- Global Spice variables

- Integration with TINACloud, files upload and download

- Optional Mechatronics extension

- KLU a faster solver on large-size circuits

- Enhanced and accelerated VHDL and Verilog simulation 10x times faster than in v9

- Xilinx simprim simulation in digital and in mixed mode

- Verilog A

- Verilog AMS

- MCU C compiling on 8051, AVR, PIC16, PIC18, PIC32, ARM

- Linux simulation on ARM MCU

- PSpice compatible AD-DA interface

- Oscilloscope settings are stored

- Oscilloscope works together with the interactive mode

- Frequency and waveform parameters are shown with cursors

- Hotkeys to AC and Transient Analysis

- Cursor Max and Min functions added to the Process menu

# 2.4 List of New features in TINA v9

- Full Vista and Windows 7 compatibility

- Multi core support for dual, quad, i7 and higher multi-core processors

- Enhanced analysis speed up to 10 times higher speed on 1 core, 15x on dual core, 20x on quad core

- Improved convergence performance based on the latest state of the art algorithms

- Advanced powerful Spice-VHDL mixed mode analysis

- Extended catalog with ARM 7, ARM 9 and HCS08 microcontrollers, more SMPS ICs models, realistic ADC and DAC models, LCD display, Bi-color LEDs

- Extended MCU simulation, USB and other modules

- Programmable Design Tool where users can implement design procedures for calculating and setting circuit parameters so that the circuits can produce predefined target output values.

- Extended flowchart tool: PIC, AVR, 8051, code box, USART, external interrupt handling

- Open and save TINA designs, models and libraries directly from the Web

- Import Spice .CIR and .LIB files directly from the Web

- Import Libraries, Examples and Designs from any earlier versions of TINA v7 and later.

- Show analysis results on diagrams during analysis

- Fast diagram drawing and processing speed, even for very large circuits

#### **PCB** Design

- G-Code export of PCB designs for creating control files for milling machines

- Revised and largely extended PCB footprint catalog

**NEW FEATURES**

New Features

# 2.5 List of New features in TINA v8

- Vista style installation and folder scheme

- Controlled sources

- Powerful Spice-VHDL co-simulation including MCUs

- Finite State Machine (FSM) editor with VHDL generation

- Flowchart editor an debubgger for controlling MCUs

- Any number of MCUs in one circuit

- Extended MCU catalog including PIC18, CAN and more

- Execution time measurement and statistics for Transient Analysis

- Hyperlinks can be added to schematics and to the diagram window

- Extended semiconductor catalog

- Application examples from Texas Instruments

- Labview based virtual instruments

- Interface to build LabVIEW based virtual instruments

- Wave (.wav) files can be used as input

- New Open Examples command in file menu to open built in examples

- Autosave. Save your current schematic or PCB design at adjustable time intervals.

- Parameter adding possibility to Spice subcircuits

- On line update possibility for libraries, program or both

- Post-processing formulas are stored with schematics, editable later

- Live 3D Breadboard (displaying and animating circuits with 3D parts on a virtual 3D breadboard)

- 3D virtual instruments to prepare and document lab experiments

- Integrated electronic design textbook with "live" circuits (optional)

- SMPS design templates from Christophe Basso (optional)

- Detection of components or nodes linked with convergence or irregular circuit problems.

# Allice Messtechnik GmbH

#### **New Features**

PCB Design (Only in TINA Design Suite v8 Edition, additional to TINA v8)

- Creating "flex" PCBs including 3D display

- Creating PCBs of any shape including round edges

- Buried and blind vias

- Extended catalog

- Improved optimizing autorouter

- Display of complete 3D circuits including parts connected externally to the PCB

# 2.6 List of New features in TINA v7

- Much faster analog solver algorithm with improved convergent properties

- Integrated VHDL support

- User defined VHDL components with VHDL source code

- VHDL components containing VHDL source code can edited and executed instantly

- MCU support including wide range of PIC processors and more

- Built in debugger and assembler compiler for MCUs

- Assembler code of MCUs can be edited and executed instantly

- External simulator and debugger for VHDL

- 3D component view in the schematic editor to review if the design is PCB ready

- Passive and active filter design

- SMPS (Switching Mode Power Supply) design support (Steady State Solver)

- Control of interactive mode from the new Interactive menu

- Stress Analysis

- Advanced integrated PCB design

Multi-layer PCBs Autoplacement

Autorouting

NEW FEATURES

# Allice Messtechnik GmbH

NEW FEATURES

Rip-up and reroute

Follow-me trace placement

DRC

Forward and back annotation

Pin/Gate swapping

Keep-in/out areas

Thermal relief,

Fanout

Gerber file output

Copper pour

Split planes

Footprint editor with multi-pin footprint wizard

3D view of PCB boards

- Support to design multi-pin schematic symbols

- More advanced Logic Design (simplification) tool

- IF statement allowed in Spice netlists

- More advanced file export (EMF, BMP, JPG) (File/Export)

- More advanced file import (EMF, WMF, BMP, JPG) (Insert/Graphics)

- Copy and Paste of any Windows dialogs (captured by Alt Prt Scr) into the Schematic Editor.

- Extended virtual instrument for real-time XY-recording, with average value, RMS calculation and recording vs. time

# CHAPTER 3 INSTALLATION AND START-UP

# 3.1 Installation Procedure

# 3.1.1 Minimum hardware and software requirements

- Intel Pentium or equivalent processor

- 1 GB of RAM

- 300 MB of available hard disk space

- CD-ROM (in case of CD ROM installation)

- Mouse or touchpad

- VGA adapter card and monitor

- Microsoft Windows XP, 7, 8, 10

- Supported Networks (for Network versions): MS Windows 2000/2003/2008/2012 Server or later, Linux Server, Novell Netware version 3.12 or later.

If the program is copy protected by a hardware key, the minimum hardware configuration includes also a USB port.

# 3.1.2 Installation from CD-ROM or from the WEB

# 3.1.2.1 Installation from CD-ROM

To begin the installation simply insert the CD into your CD-ROM drive. The Setup Program will start automatically if the Auto-Run function of your CD-ROM has been enabled (Windows-Default). If not, Select Start/Run and type:

D:SETUP (Enter) (where D represents your CD-ROM drive).

The setup program will start.

# 3.1.2.2 Installation from the WEB

If you have purchased a downloadable version of TINA you need to download it using the download link sent by email after your successful purchase.

Windows usually saves downloaded files in the Downloads folder which is located under your user name in the **users** folder on the drive where Windows is installed (for example C:\users\**your name**\downloads). Double-click the file to start the setup. If you purchased the Mechatronics add-on package, you should install it separately after installing TINA.

NOTE:

This software may come with copy protection. For further details see the Copy Protection and the Network Installation sections.

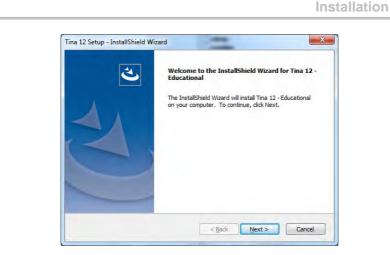

# 3.1.3 Following the Installation Steps

TINA's Setup Procedure follows the steps standard with most Windows Programs. There are several screen pages where you can enter or change important installation choices, such as Type of Installation, Destination Directory, etc. To continue installation, click on <u>Hero</u>. You can always step back, using the <u>Hero</u>-Button. If you do not want to continue installation for any reason, click on <u>Hero</u>. If you elect to cancel installation, the program will ask you if you really want to exit. At this point you can either resume or exit Setup.

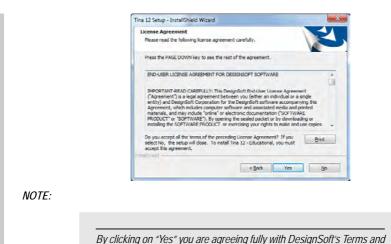

# 3.1.4 Welcome and Software License Agreement

To begin the Procedure click on Next on the Welcome Page. The first step is the Software License Agreement.

# Allice Messtechnik GmbH

#### Installation

# 3.1.5 Entering User Information

Conditions for using this software.

This data is used to personalize your copy of the software. By default, the installation program picks up the data entered when you set up Windows. You accept these names as defaults by clicking on Next or you can change them.

Depending on your program version you might also need to enter a Serial Number located on your CD-ROM package or on your Quick Start Manual.

| ustomer Information            |                                        |        |

|--------------------------------|----------------------------------------|--------|

| Please enter your information. |                                        |        |

| Please enter your name and the | e name of the company for which you wo | rk.    |

|                                |                                        |        |

| User Name:                     |                                        |        |

| Your Name                      |                                        |        |

| Company Name:                  |                                        |        |

| Your Company                   |                                        |        |

|                                |                                        |        |

| The conjunt                    |                                        |        |

| The conjunt)                   |                                        |        |

| Tool Conferral                 |                                        |        |

|                                |                                        |        |

| talsoeld                       | < Bork Next                            | Cancel |

INSTALLATION

#### Installation

# 3.1.6 Platform Selection

The installer **includes both 32-bit and 64-bit TINA versions**. It will automatically choose the right version to install.

If you have 64-bit Windows and want to install 32-bit TINA version you can select the 32-bit version but not vice versa. Click on to continue.

# 3.1.7 Single User License and Networking Options

#### 3.1.7.1 Single user license (installed on a local PC)

Select this option if you have a single user license and want to use a single copy of TINA on a local PC.

However if you purchased a network license and want to use TINA in a network environment you can choose between 2 options.

#### Installation

#### 3.1.7.2 Network license installed on local PCs

Select this option if you want to use the server as a license server. In this case the server stores the license information and the software is installed on the workstations. After you've installed the package on the first workstation start TINA and select the location of the license information file on the file server then authorize the package. Finally install the software on every other workstation (client) where you want to use TINA. On these stations when you start TINA for the first time you have to locate the license file on the server.

No other authorization is required.

#### 3.1.7.3 Network license installed on file server

Select this option if you want to use the server as a file server. In this case the server store the files of the software and the license information as well. You have to select a network share in the destination dialog of the setup and install the package there. Next you have to install the package on the first workstation and authorize it. Select the Run commands from the Windows Start menu, enter the command U:\Tina\NWSetup\setup, where U: represents your network drive, and follow the instructions. Note that TINA is the main program directory holding TINA on the server. Start TINA on the first workstation.

Note that when you authorize the first workstation full access is needed on the network share where TINA is located. Authorize TINA.

#### Installation

Finally you must run the setup program on every other workstation (client) where you want to use TINA. No authorization is required on these stations.

# 3.1.8 Choose Destination Location

Here you can select an Installation Directory other than the one suggested as a default. The default is the Windows Standard Directory for Programs. To change the directory, click on Browse and select a different drive and/or directory from the Choose Folder Dialog.

| hoose Destination Location<br>Select folder where setup will inst | tall files.                           |                        |

|-------------------------------------------------------------------|---------------------------------------|------------------------|

| Setup will install Tina 12 - Education                            | onal in the following folder.         | -                      |

| To install to this folder, dick Next another folder.              | . To install to a different folder, o | lick Browse and select |

|                                                                   |                                       |                        |

|                                                                   |                                       |                        |

|                                                                   |                                       |                        |

| Destination Folder                                                |                                       |                        |

| Destination Folder<br>C:\Program Files\DesignSoft\Tir             | na 12 - Educational                   | Browse                 |

|                                                                   | na 12 - Educational                   | Browse                 |

#### IMPORTANT NOTE:

If you are installing TINA for Windows to a hard disk that already has an earlier version of TINA, you must be sure to use a new directory name for TINA for Windows, such as the suggested directory, C:\Program Files\DesignSoft\Tina, or the working files you have already created will be overwritten and lost. If uncertain, exit setup, copy your TINA files safely to another hard disk directory or to floppy disks, then resume setup.

#### Installation

# 3.1.9 Selecting a Setup Type

TINA offers you three different types of Setup. You can either run a Typical Setup (Default) a Compact Setup or a Custom Setup.

| Setup Type<br>Select the set | up type to install.                                                                 |

|------------------------------|-------------------------------------------------------------------------------------|

|                              | of setup you prefer, then click Next.<br>m Setup to install the TINALab hardware.   |

| Typical                      | Program will be installed with the most common options. Recommended for most users. |

| © <u>C</u> ompact            | Program will be installed with minimum required options.                            |

| Custom                       | You may select the options you want to install. Recommended for advanced users.     |

| tallShield ——                | < Back Next > Cancel                                                                |

NOTE:

The detailed settings for the Compact installation are made after you select Compact and click on Next.

# 3.1.9.1 Typical

The commonly used components are installed. This includes Program Files, Samples and Utilities (i.e. Exam Manager, Spice Library Manager).

### 3.1.9.2 Compact

Only the most important components are installed. This results in a usable TINA installation, but one without certain program components, such as Exam Manager.

Installation

#### 3.1.9.3 Custom

You will be able to decide which components are to be installed. The default settings are similar to those of the Typical installation. Deselect the unwanted components or select the missing ones.

NOTE:

If you wish to install the TINALab Card, TINALab II or other third party supplementary hardware, you must select the Custom installation option at the time of installation and check the appropriate device driver on the list.

# 3.1.10 Selecting the Program Folder

Here you can choose where in the Programs Section of your Windows Start Menu the Program Icons will appear. The default is a new sub menu called for example TINA 11 – Industrial. You can change this name or select an existing Program Folder from the list.

# www.allice.de

# Allice Messtechnik GmbH

| -  |             |              |          |    |    |

|----|-------------|--------------|----------|----|----|

| 10 | <b>O</b> +4 | <u> – II</u> | $\sim +$ | in | 10 |

|    | Sta         |              |          |    |    |

|    | ~~~         | MIN I        | ~ ~      |    |    |

| Select Program Folder<br>Please select a program folder.                                                 |                                                                                                    |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                                                                                          | Program Folder listed below. You may type a new folden<br>ng folders list. Click Next to continue. |

| Program Folder:                                                                                          |                                                                                                    |

| Tina 12 - Educational                                                                                    |                                                                                                    |

| Existing Folders:                                                                                        |                                                                                                    |

| Accessories                                                                                              |                                                                                                    |

| Administrative Tools<br>Adobe<br>Adobe LiveCyde ES2<br>Audio Related Programs<br>AVAST Software<br>Avery | Į                                                                                                  |

| Camtasia Studio 7<br>DeepBurner                                                                          |                                                                                                    |

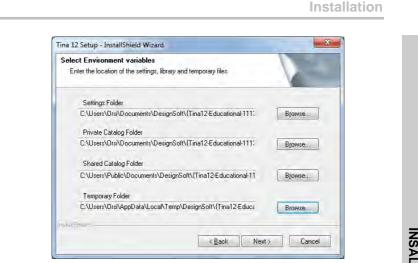

# 3.1.11 Select Environment Options

In TINA you can set up the settings, private/shared catalog and temporary folder. The Settings folder stores your personal settings. The private catalog folder will store your catalog files, while the shared catalog folder can be used to share catalog files with other users of the same PC or with other users in the network. The temporary folder stores the temporary files of the software. By default these folders are set to common Windows folders however you may change the folders by pressing the browse button.

# 3.1.12 Selecting the Symbol Set

TINA can display its component schematic symbols according to the US (ANSI) or the European (DIN) conventions. Select the one appropriate for you.

| Select Symbol Set               |                  | 14        |

|---------------------------------|------------------|-----------|

| Select the schematic symbol set | you want to use: |           |

| O US (ANSI)                     |                  |           |

| 🔘 European (DIN)                |                  |           |

|                                 |                  |           |

|                                 |                  |           |

|                                 |                  |           |

|                                 |                  |           |

|                                 |                  |           |

| tallShield                      | Local States     |           |

|                                 | < Back Nex       | t> Cancel |

INSALLATION

INSTALLATION

#### Installation

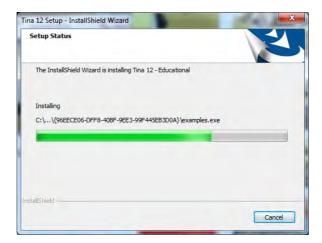

# 3.1.13 Final check and copying the files

This page lists the settings you have made, giving you an opportunity to check these settings and alter them and step back if changes are necessary. After you click on Next, the Setup Program starts copying the files automatically.

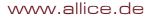

# 3.1.14 Completing the Setup

After all the selected files have been copied and the Start Menu entries created, you are asked if you want to place a Shortcut to the TINA program file on your Desktop. The last page indicates a successful installation and invites you to open and read a file with the latest information about TINA. We urge you to take a moment and review that file. Click on finish when you're ready.

Installation

NOTE:

You can read the latest information in the file again at any time by selecting Read Me from the Tina Start Menu Entries. You can also get the latest information about changes or new features by visiting our Web Site, www.tina.com.

# 3.2 Uninstalling TINA

You can uninstall TINA at any time. Note that this will not delete files you have created.

- 1. To begin Uninstallation locate Uninstall Tina on the Start or Apps screen of Windows 8 or in the Start Menu of earlier Windows versions.

- 2. Click on Uninstall Tina.

- 3. In the next dialog click on Yes if you are positive you want to uninstall TINA.

#### Installation

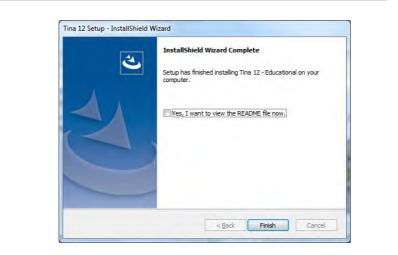

# 3.3 Maintaining or Repairing an Installation

You can modify or repair an existing installation of TINA as follows: Select Settings and Control panel from the Start menu of Windows. Click on the Add or Remove programs icon. Locate your TINA installation on the list and press the Change button (Press the Remove button if you want to uninstall the software). The installer of TINA will start and you can either modify the existing installation by adding or removig components or repair the current installation or uninstall the pacakage.

# 3.4 Network Installation

To install the Network version of TINA, you must have administrative privileges on the server machine and you have to share a disk volume or directory on your network, the place where TINA will be installed. With file sharing users can access TINA files. The share must be writeable by the administrator user during the installation process.

Therefore, carry out the following steps to make all files in the specified directory shared:

#### Installation

**Novell Netware 3.x:** Logon to the server and perform the following commands:

FLAG \*.\* S SUB

Novell Netware 4.x and later versions:

FLAG \*.\* +SH /S

Linux server: You need Samba, a free software suite to provide file services for Windows clients. Logon as root and create a Samba share directory on your Linux system, adding the following section to your /etc/samba/smb.conf file, then restart Samba service. Example:

[TINA]

comment = TINA install folder

path = /TINA

writeable = yes

admin users = administrator root

valid users = TINAUserGroup

read list = TINAUserGroup

store dos attributes = yes

Later, you might have problem mapping Linux Samba shares to Windows Vista/7 client. Then check Vista LAN Manager authentication level: open the Run command and type "secpol.msc" and click OK. Go to Local Policies, Security Options and navigate "Network Security: LAN Manager authentication level" and open it. Change the settings from "Send NTLMv2 response only" to "Send LM & NTLM - use NTLMv2 session security if negotiated". Once you have done this, Windows Vista will be able to view network drives based on Samba servers.

**Windows Server:** Logon as Administrator and use the NET SHARE command, for example:

NET SHARE TINAFolder="C:\Program Files\DesignSoft\TINA"

Or, you can use the Windows Explorer:

- 1. Right-click the drive or folder, and then click Sharing and Security.

- 2. Select the "Share this folder" option and type a Share name.

# www.allice.de

#### Installation

3. Click the Permissions button and ensure that the administrator have Full control permission and click OK twice.

#### Windows Client:

Next make sure that the clients have a mapped drive set to the network drive containing the TINA program folder.

To assign (map) a drive letter to a network computer or folder do the following:

- 1. Open Windows Explorer

- 2. On the Tools menu, click Map Network Drive.

- 3. In Drive, select a drive letter, e.g.: G:

- 4. In Path (Win9x/Me) or Folder (NT/2000/XP/Vista/7), select from the drop-down list or type in the network drive (server and share name: \\MyServer\Volume1) or folder name to which you want to assign (map) a Drive letter (\\MyServer\Volume1\Program Files\DesignSoft\TINA). Note, that share name refers to a shared folder on the server. On Windows NT/2000/XP/Vista/7 you can use Browse to find the network computer, drive and folder.

- 5. Set the Reconnect at Logon checkbox, then press OK.

Then execute the installation procedure directed by section 3.1.1 on the mapped disk volume, that is accessible from the network.

After you have set everything up on the network disk according to the instructions above, you must run the setup program on each client where you want to run TINA. Start setup.exe (in some versions nsetup.exe) from the TINA\NWSETUP directory.

When you run setup.exe you must specify the working directory which should be located on a local drive of the workstation.

The working directory can be on the network; however in this case the path of this directory must be different on every work station. After you've specified the working directory, you may install the optional measurement hardware for TINA (e.g TINALab). After running setup.exe, you will be able to run TINA simultaneously on any number of workstations, just as though each workstation had a single user version.

Network versions are copy protected and need authorization. For the details regarding the special procedures required for authorizing networked computers, refer to section 3.5.

Installation

# 3.5 Copy Protection

Executing the authorization procedure described in this section, you will be able to run TINA. If you use a network version of the program, you will be able to do it simultaneously on the number of workstations the program licensed, just as though each workstation had a single user version.

# 3.5.1 Copy protection by Software

If your version of TINA is copy-protected by software you need to authorize it.

You have to be in Administrator mode when you authorize the program.

#### NOTE FOR VISTA AND WINDOWS 7 AND 8:

Even though you are a user configured as an "Administrator", Vista and Windows 7 treats you as a standard user so the authorization may not succeed unless you make sure that User Account Control (UAC) is enabled in Vista. This is enabled by default, so if you didn't turn it off manually it should be OK. (You can find this setting in the Control Panel when you enter 'UAC' in the search field in the upper right corner of the Window.)

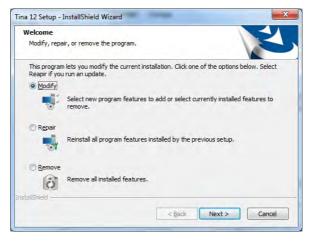

Authorize the program with the following steps:

1. Run Authorization & Trial from the Start or Apps screens of Windows 8 or from the TINA group of the Start menu.

2. The Authorization Manager dialog will appear.

# www.allice.de

# Allice Messtechnik GmbH

#### Installation

In most cases you should just press OK to continue. The License Status dialog will appear showing your initial authorization status.

If the program starts but the License Status dialog does not appear, select the Authorization/ Authorize from the Help menu of the Schematic Editor. You will normally have 31 trial sessions to provide you enough time obtain the authorization.

|                       | TINA<br>.333 SF-DS |

|-----------------------|--------------------|

| Copyright 199         | 3-2018 DesignSoft  |

| License status:       | Unregistered       |

| Max concurrent users: | ?                  |

| License type:         | Local              |

| Remaining trial runs: | 0                  |

- Press the Authorize button on the License Status dialog which is displayed at program start or select Authorization/Authorize from the Help menu of TINA.

- Enter your 16 digit Order number into the Order number field of the Authorize dialog appearing and press OK. For successful operation you must be connected to the Internet and your firewall should allow communication with our server.

### www.allice.de

# Allice Messtechnik GmbH

#### Installation

- If the above is not possible for any reasons select the Other tab on the Authorize dialog.

- Email your Site code to DesignSoft using the link in the Authorize dialog or contact your dealer.

- We will email back a Site key, which should be copied into the Site key field of the Authorize dialog.

- Press OK to finish the authorization.

#### NOTE FOR NETWORK VERSION:

If you use a network version of Tina then it will run on workstations where the setup with the NWSETUPISETUP.EXE program has already been done. It is sufficient to authorize the software at one workstation. This will allow to run the software simultaneously, as long as the total number of simultaneous users does not exceed the licensed number. In some cases the program comes with a Serial number, which needs to be entered during installation. When entering the serial number you do not need an active internet connection. For more information refer to the program's Authorization Help by pressing the Help button.

#### Authorization in secure environment

If you started the program with the "Authorization and Trial" command but you still get the "Please log on with administrator privileges!" message it is a sign that you have a secure environment and need a special installation. This may be the case in systems at larger companies.

In this case select Mode: "Authorization in secure environment" in the Authorization Manager dialog. However you need to consult with DesignSoft or with your dealer and ask for a special Order number before you continue.

# 3.5.2 Copy Protection by Hardware (dongle)

# 3.5.2.1 Single user version

Make sure you are in Administrator mode.

If you have a USB dongle-protected version of TINA, install TINA first before connecting the dongle.

Next, connect the dongle to the USB port. The dongle driver installation will begin. If Windows looks for the dongle driver, select the recommended option, which is your hard disk.

If the dongle is not connected or not installed correctly the following error message will appear:

```

Hardware protection key is not present (USB).

```

# 3.5.2.2 Site license with multi-user dongle (DSPROTKEY)

To avoid loss or damage of dongles you may have just one dongle for a whole site. In this case you need the dongle only at the first start of the program at each workstation.

1) Install the software on each computer as described in the manual for single computers, according to the number of licenses purchased for your site.

2) Start the program with the dongle plugged in, then close the program and remove the dongle. After you authorized all workstations this way keep the dongle at safe place. If on some workstations the license is lost for any reasons (e.g. disk crash), you can reinstall the program and authorize again with the same technique. Please do not use this possibility to install the software on more workstations than licensed, because this might eliminate the possibility to recover lost licenses.

# 3.5.2.3 Authorization with network dongle

If you have a network dongle do the following to authorize TINA on the server.

1. After setting up the workstations (see section 3.4), login on one workstation as Administrator (with writing right to the volume where TINA resides).

#### Installation

2. Connect the dongle with the above workstation. The system must recognize the dongle and the LED on the dongle should light.

3. Start TINA. Based on the information in the dongle TINA will be authorized for the number of users licensed, and a dialog box should appear to confirm this.

4. Remove the dongle and keep it at a safe place, as you may need it to recover the license in case of a system crash.

5. Now TINA should run on all workstations without the dongle.

# 3.6 Starting Up

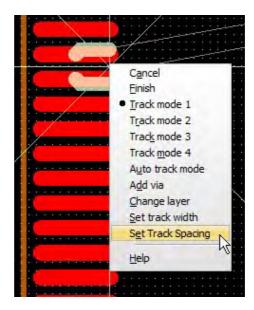

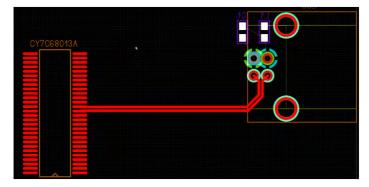

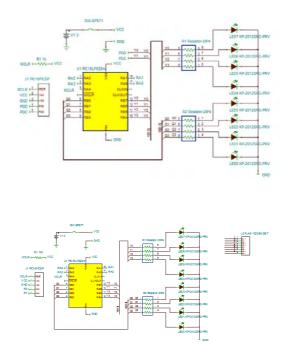

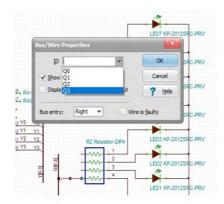

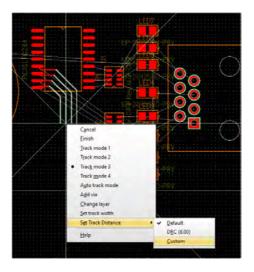

After successfully installing TINA, you can start the program by simply double-clicking the TINA icon on your Desktop or by choosing Tina from the TINA Start Menu Entries.